Author: Jian Wang and Tamara Schmitz

# Development of a Voltage Feedback Spice Op-Amp Macromodel

## Introduction

A voltage-feedback amplifier macromodel has been developed that simulates the most common effects, such as transient response, frequency response, voltage noise and input/output slew rate limiting. Detailed descriptions of each stage in the model will be presented with examples of model performance and correlation to actual device behavior.

Macromodels are developed for the customer instead of releasing full transistor schematics. Of course, the most accurate simulations are conducted from fully-extracted 3-D device models. Not only would it be impractical to share these models because of the need to accommodate the numerous simulation platforms, but also because of proprietary reasons.

One of the first op-amp macromodel techniques was developed by Boyle in 1974 and used only two transistors, a few diodes and linear elements [1]. Linear elements like resistors, capacitors, inductor and voltage/current control sources simulate much faster than active elements and are used to provide poles, zeros and any gain. For a DC model, a voltage-controlled voltage source can represent the amplifier while resistances can be added to better represent the input and output impedance. Capacitors, inductors, diodes and transistors can then provide the proper AC response. If you want more information on the development of simulation models, see Alexander and Bowers [2] and [3]. We will follow their model here.

#### **The ISL28133**

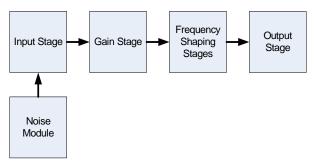

As an example, we are going to investigate the ISL28133. The ISL28133 is a zero-drift operational amplifier with voltage feedback topology. Intended for low frequency and power precision applications, the gain bandwidth product is 400kHz, the slew rate is  $0.1V/\mu s$  and the supply current is  $18\mu A$ . A five-stage model represents the actual circuit, the block diagram for which is shown in Figure 1. They are the input stage, the gain stage, the frequency-shaping stage, the output stage and the noise module.

FIGURE 1. THE BLOCK DIAGRAM OF ISL28133 MACROMODEL

1

#### **The Input Stage**

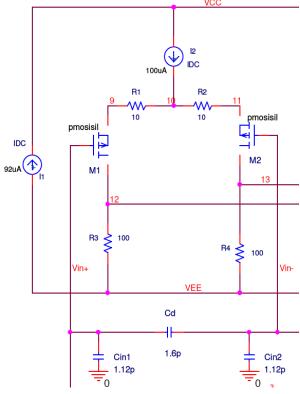

The input stage of the zero-drift amplifier is shown in Figure 2. The 100 $\mu$ A current source 'I2' feeds the PMOS input pair. Normally, I2 should be chosen less than the quiescent current. Remember, the ISL28133's typical supply current (RL = open) is only 18 $\mu$ A. However, a small I2 (~10 $\mu$ A) would make the input voltage noise too large to emulate. This will be discussed later in the noise analysis part. Choose I2 = 100 $\mu$ A and use I1 to compensate back to the total quiescent current. Cin1 and Cin2 are the input common mode capacitance and Cdiff is the input differential mode capacitance.

FIGURE 2. INPUT STAGE

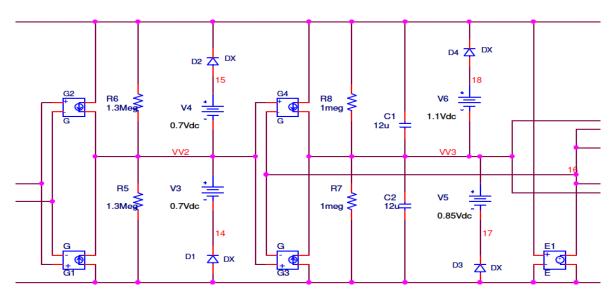

### The Gain Stage (Figure 3)

This stage performs some important functions in the model:

- 1. This stage sets the DC gain of the part. All the subsequent stages provide unity DC gain.

- 2. It provides slew rate limiting.

- 3. It adds the dominant pole to the AC characteristic.

- It level shifts the signal from two voltages referred to the supplies to a single voltage referred to the mid-point.

- 5. It limits the full scale output swing.

FIGURE 3. GAIN STAGE

Referring to Figure 3, Ga is the gain of block  ${\tt G1}$  and  ${\tt G2}$ . Gb is the gain of block  ${\tt G3}$  and  ${\tt G4}$ .

$$SlewRate = \frac{I2 \bullet R3 \bullet Ga \bullet R5 \bullet Gb}{C1}$$

(EQ. 1)

Changing the value of V3 and V4 limits the slew rate. Also, R8/C1 and R7/C2 decide the dominant pole of this model. E1 is used to set the reference level at the middle of Vcc and Vee.

#### **Frequency-Shaping Stages**

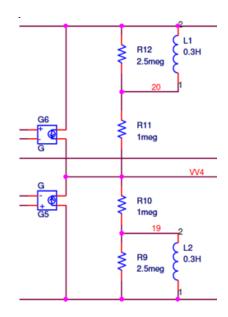

The "telescopic" frequency shaping techniques used here are very common in op-amp modeling. It is easy to add more poles and zeros. Each frequency-shaping block provides unity gain. A zero-pole pair is included in this model and shown in Figure 4.

$$R10 = R11 = 1M\Omega \tag{EQ. 2}$$

$$R9 = R12 = R10 \cdot (\frac{f_p}{f_z} - 1)$$

(EQ. 3)

$$L1 = L2 = \frac{R9}{2\pi f_p}$$

(EQ. 4)

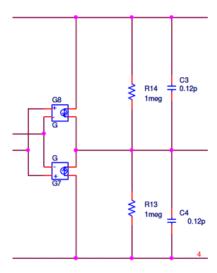

A higher order pole stage is shown in Figure 5, G7/8, R13/14 and C3/4.

FIGURE 4. ZERO-POLE PAIR STAGE

FIGURE 5. HIGHER ORDER POLE STAGE

#### **Noise Simulation**

The ISL28133 input current noise is very small (~70fA), so it is neglected in this model. The voltage noise of the MOSFET can be modeled like the following equations.

$$V_i^2(f) = 4kT(\frac{2}{3})\frac{1}{g_{in}} + \frac{K}{WLC_{out}f}$$

(EQ. 5)

$$g_{\scriptscriptstyle m} \propto \sqrt{I_{\scriptscriptstyle D}}$$

(EQ. 6)

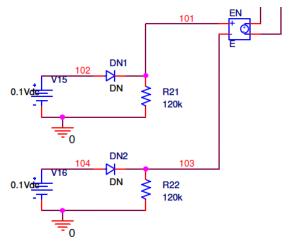

I<sub>D</sub> is the drain current. High bias current in the model is needed to emulate the low voltage noise. At the input stage, the tail current is set high enough to generate the low input voltage noise. Before the noise sources are added, the model has to be rendered lower noise than the spec or typical performance noise curve in the <a href="datasheet">datasheet</a>. The noise-voltage module of Figure 6 generates 1/f and white noise by using a 0.1V voltage source biasing a diode-resistor series combination. White noise is generated by the thermal noise-current.

$$i_n^2 = \frac{4kT}{R} \tag{EQ. 7}$$

where k is the Boltzmann's constant. So, the required value of the resistor for a given noise-voltage spectral density is:

$$R = \frac{e_n^2}{2 \times 4kT} \tag{EQ. 8}$$

where  $\mathbf{e}_n$  is the spectral density of the white noise voltage. The design of the chopper stabilized amplifier greatly reduced 1/f noise. 1/f noise (flicker noise) refers to the noise exhibiting power spectral density inversely proportional to the frequency. More generally, the noise with the spectral density

$$S_N \propto \frac{1}{|f|^{\beta}} \quad \beta > 0$$

(EQ. 9)

is also called 1/f noise. Normally, the frequency where the flicker noise curve crosses the white noise curve is defined as the corner frequency. The small amount of flicker noise that remains is modeled within the SPICE diode model. Referring to Figure 6,

$$i_n^2 = 2qI_d + KF \bullet \frac{I_d^{AF}}{frequency}$$

(EQ. 10)

Id is the DC diode current. AF and KF are the model parameters of the SPICE diode and q is the charge of the electron. The flicker noise exponent (AF) is set to 1 and the flicker noise coefficient (KF) is set

$$KF = \frac{E_a^2}{2R^2 \bullet I_d} \tag{EQ. 11}$$

where Ea is the noise-voltage spectral density at 1Hz. The simulated voltage noise will show the 1/f noise-voltage spectral density with the correct corner frequency.

FIGURE 6. NOISE VOLTAGE MODULE

#### **Output Stage**

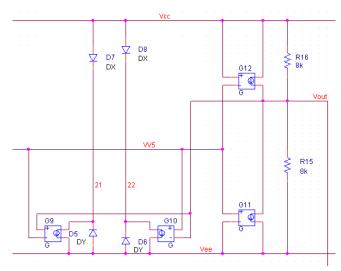

After the frequency shaping-stages, the signal appears at Node VV5, which is referenced to the midpoint of two supply rails. Each controlled source can generate enough current to support the desired voltage drop across its paralleled resistor. R15 and R16 are equal to twice of the open loop output resistance, so their parallel combination gives the correct Zout. D5-D8 and G9/10 are used to force a current from the positive rail to the negative rail to correct the real current sink or source in the supply pins.

$$G9 = G10 = G11 = G12 = \frac{1}{2Z_{out}}$$

(EQ. 12)

$$R15 = R16 = 2Z_{out}$$

(EQ. 13)

# **Application Note 1685**

FIGURE 7. OUTPUT STAGE

#### **Simulation Results**

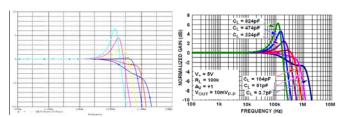

Some SPICE simulation results are compared with the typical performance curve from the datasheet in the following. (Figure 8b is from the datasheet).

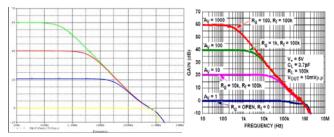

FIGURE 8. GAIN vs FREQUENCY vs LOAD CAPACITANCE. IT CANNOT BE VERY ACCURATE BECAUSE THE PARASITIC CAPACITANCE ON THE BOARD WASN'T INCLUDED IN THE MODEL. THE ERROR IS LESS THAN 5%

FIGURE 9. FREQUENCY RESPONSE OF CLOSED LOOP GAIN WITH DIFFERENT GAIN. AT GAIN = 100, THE BANDWIDTH IS 3.94kHz AND THE ERROR IS LESS THAN 5%. AT LOW GAIN, THE BANDWIDTH IS EXPANDED BECAUSE OF THE ZERO POLE PAIR

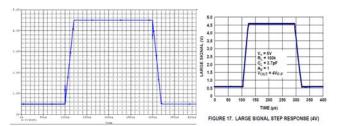

FIGURE 10. LARGE SIGNAL STEP RESPONSE. THE SLEW RATE SIMULATED IS 0.198V/ $\mu s$  AND THE ERROR IS 1%

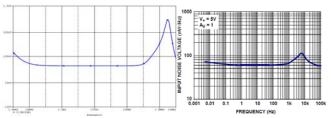

FIGURE 11. INPUT NOISE VOLTAGE vs FREQUENCY. AT 1kHz, THE SIMULATED INPUT NOISE VOLTAGE IS 64.9 nV/Hz, VERY CLOSE TO THE VALUE IN THE DATASHEET 65nV/Hz. THE SIMULATED CURVE CANNOT CATCH THE PEAK NEAR 10kHz

# **Conclusion**

A truly comprehensive SPICE macromodel for a voltage feedback amplifier is developed. This macromodel includes effects such as transfer response, accurate AC response, DC offset and voltage noise. It is easy to add more features like CMRR, PSRR, input current-noise, etc. Also it is convenient to change the parameters of the model to fit other voltage feedback amplifiers. Actually, several of Intersil's voltage feedback amplifiers use the same model topology.

# **ISL28133 Macromodel Netlist**

- \* ISL28133 Macromodel

- \* Revision B, July 2009 by Jian Wang

- \* This model simulates AC characteristics, Voltage Noise, Transient Response

- \* Connections: +input -input +Vupply -Vsupply Vout

.subckt ISL28133 3 2 7 4 6

\*Input Stage

C\_Cin1 80 1.12p C\_Cin2 20 1.12p C\_Cd 8 2 1.6p R\_R1 9 10 10 R\_R2 10 11 10 R R3 4 12 100 R\_R4 4 13 100  $M_M1$ 12899 pmosisil

+ L=50u

# **Application Note 1685**

| + W=50u              |                       | C_C4     | 4 VV5 0.12p                     |  |

|----------------------|-----------------------|----------|---------------------------------|--|

| M_M2                 | 13 2 11 11 pmosisil   | R_R13    | 4 VV5 1meg                      |  |

| + L=50u              |                       | R_R14    | VV5 7 1meg                      |  |

| + W=50u              |                       | *Output  | *Output Stage                   |  |

| I_I1                 | 4 7 DC 92uA           | G_G9     | 21 4 6 VV5 0.0000125            |  |

| I_I2                 | 7 10 DC 100uA         | G_G10    | 22 4 VV5 6 0.0000125            |  |

| *Gain stage          |                       | D_D5     | 4 21 DY                         |  |

| G_G1                 | 4 VV2 13 12 0.0002    | D_D6     | 4 22 DY                         |  |

| G_G2                 | 7 VV2 13 12 0.0002    | D_D7     | 7 21 DX                         |  |

| R_R5                 | 4 VV2 1.3Meg          | D_D8     | 7 22 DX                         |  |

| R_R6                 | VV2 7 1.3Meg          | R_R15    | 4 6 8k                          |  |

| D_D1                 | 4 14 DX               | R_R16    | 6 7 8k                          |  |

| D_D2                 | 15 7 DX               | G_G11    | 6 4 VV5 4 -0.000125             |  |

| V_V3                 | VV2 14 0.7Vdc         | G_G12    | 7 6 7 VV5 -0.000125             |  |

| V_V4                 | 15 VV2 0.7Vdc         | *Voltage | Noise                           |  |

| *SR limit first pole |                       | D_DN1    | 102 101 DN                      |  |

| G_G3                 | 4 VV3 VV2 16 1        | D_DN2    | 104 103 DN                      |  |

| G_G4                 | 7 VV3 VV2 16 1        | R_R21    | 0 101 120k                      |  |

| R_R7                 | 4 VV3 1meg            | R_R22    | 0 103 120k                      |  |

| R_R8                 | W3 7 1meg             | E_EN     | 8 3 101 103 1                   |  |

| C_C1                 | VV3 7 12u             | V_V15    | 102 0 0.1Vdc                    |  |

| C_C2                 | 4 VV3 12u             | V_V16    | 104 0 0.1Vdc                    |  |

| D_D3                 | 4 17 DX               | .model p | mosisil pmos (kp=16e-3 vto=10m) |  |

| D_D4                 | 18 7 DX               | .model D | .model DN D(KF=6.4E-16 AF=1)    |  |

| V_V5                 | VV3 17 0.7Vdc         | .MODEL I | .MODEL DX D(IS=1E-18 Rs=1)      |  |

| V_V6                 | 18 VV3 0.7Vdc         | .MODEL I | DY D(IS=1E-15 BV=50 Rs=1)       |  |

| *Zero/Pole           |                       | ends ISL | .ends ISL28133                  |  |

| E_E1                 | 16 4 7 4 0.5          |          |                                 |  |

| G_G5                 | 4 VV4 VV3 16 0.000001 |          |                                 |  |

| G_G6                 | 7 VV4 VV3 16 0.000001 |          |                                 |  |

| L_L1                 | 20 7 0.3H             |          |                                 |  |

| R_R12                | 20 7 2.5meg           |          |                                 |  |

| R_R11                | VV4 20 1meg           |          |                                 |  |

| L_L2                 | 4 19 0.3H             |          |                                 |  |

| R_R9                 | 4 19 2.5meg           |          |                                 |  |

| R_R10                | 19 VV4 1meg           |          |                                 |  |

| *Pole                |                       |          |                                 |  |

| G_G7                 | 4 VV5 VV4 16 0.000001 |          |                                 |  |

| G_G8                 | 7 VV5 VV4 16 0.000001 |          |                                 |  |

| C_C3                 | VV5 7 0.12p           |          |                                 |  |

|                      |                       |          |                                 |  |

# **Application Note 1685**

# References

- [1] BOYLE, G.R., "Macromodeling of integrated circuit operational amplifiers", IEEE J. 1974, SC-9.

- [2] Derek Bowers, Mark Alexander, Joe Buxton, "A Comprehensive Simulation Macromodels for 'Current Feedback' Operational Amplifiers," IEEE Proceedings, Vol. 137, April 1990 pp.137-145

- [3] Mark Alexander, Derek Bowers, "AN-138 SPICE-Compatible Op Amp Macro-Models", Analog Devices Inc., Application Note 138.

- [4] "AN-840 Development of an Extensive SPICE Macromodel for 'Current-Feedback' Amplifiers", National Semiconductor Corp., Application Note 840.

Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that the Application Note or Technical Brief is current before proceeding.